8 Bit Serial To Parallel Converter Verilog Code

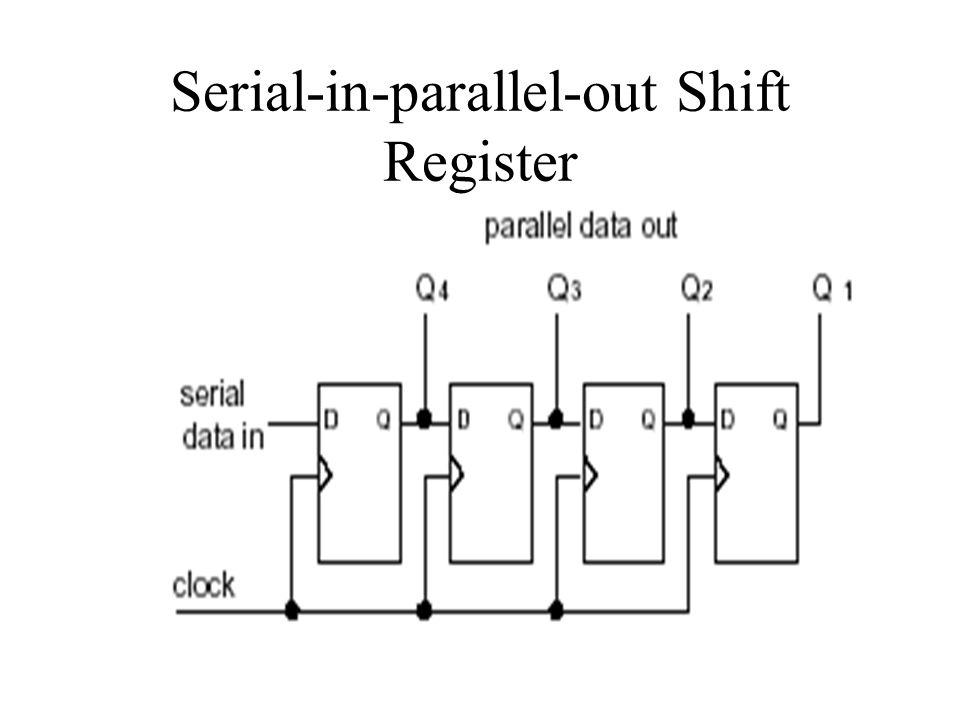

Primeri smet na proektnie raboti kapitaljnij remont rezervuara nefti. Design of Serial IN - Parallel Out Shift Register using Behavior Modeling Style - Output Waveform: Serial IN - Parallel OUT Shift Register Verilog CODE- //----------------------------------------------------------------------------- // // Title: SIPO // Design: verilog upload 2 // Author: Naresh Singh Dobal // Company: nsdobal@gmail.com // Verilog Programs & Exercise by Naresh Singh Dobal. // //----------------------------------------------------------------------------- // // File: Serial IN Parallel OUT Shift Register using Behavior Modeling Style.v module SIPO ( din,clk,reset,dout ); output [3:0] dout; wire [3:0] dout; input din; wire din; input clk; wire clk; input reset; wire reset; reg [3:0]s; always @ (posedge (clk)) begin if (reset) s.

2 bit serial to parallel conversion VHDL source code. This page of VHDL source code covers 2 bit serial to parallel conversion vhdl code and provides link to 2 bit parallel to serial conversion.

Design and implementation of 8 bit serial/ parallel input serial output shift register using behavioral style of modelling. I'm using 74LS166 8-BIT SHIFT REGISTERS IC. This code is serial input serial output but not sure. Plz check it? Shall you provide or type the code of parallel input serial output?? Library ieee; use ieee.std_logic_1164.all; entity SReg is generic ( n: integer:= 4 ); port( clk: in std_logic; reset: in std_logic; enable: in std_logic; --enables shifting parallel_in: in std_logic_vector(n-1 downto 0); s_in: in std_logic; --serial input s_out: out std_logic --serial output ); end SReg; architecture behavioral of SReg is signal temp_reg: std_logic_vector(n-1 downto 0):= (Others => '0'); begin process (clk,reset) begin if (reset = '1') then temp_reg.